As a prequel to my upcoming FusionIO performance benchmarking articles I thought I would quickly demonstrate how easy it is to install the FusionIO drivers for VMware ESXi.First you need to download the drivers from, you will need to register to access the support website.Once you login you need to click the Downloads button and you will see the “Identify Product” section appear similar to the below. Fusion io drivers windows 10.

QCAD is one free CAD software for Mac that allows the user to paste clipboard sections cut or copied out of other functions/designs and also manipulate the view by rotation, flipping, or scaling actions. Technical designs may range across any measurement units with this software - starting from mile to micron. If you’re looking for something powerful for 2D CAD design but amazingly easy to use and value for money, SmartDraw is the best 2D CAD software for Mac on the market. Free easy cad software mac.

This tutorial is the simulation only & extension to my detailed video on 8:1 Mux.

Ytd video downloader 3.9.6 serial key free download. In this tutorial, I have designed a 8:1 MUX using dataflow, behavioral & structural modeling to verify its functionality using Xilinx ISE software. Mac os x lion dmg google drive. As a part of VTU syllabus, This tutorial will. Verilog Code For 8 To 1 Multiplexer Using Dataflow Modelling I can only guess how on earth have you ended up with ’character in your code as it is not that easy to type in (i.e. On Mac you have to hold Shift+Option+). At any rate, that character is a Unicode 0xE28099and is not a legal Verilog code.

- This tutorial is the simulation only & extension to my detailed video on 8:1 Mux.

- 8 to 1 Multiplexer HDL Verilog Code. This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using verilog. Following is the symbol and truth table of 8 to 1 Multiplexer.

Introduction

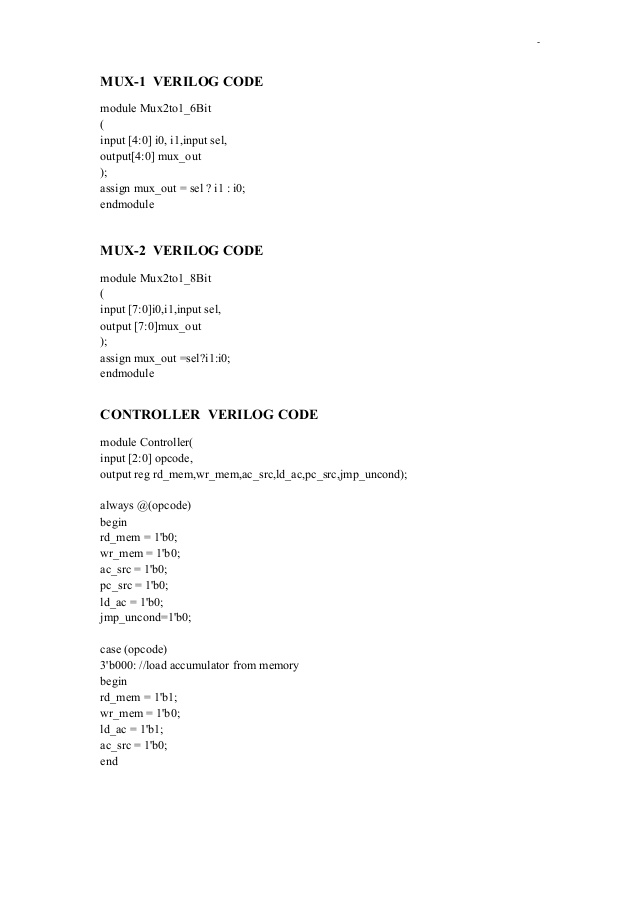

An 8-to-1 multiplexer is a digital device that selects one of the eight inputs lines to the output line by using three-bit selection line. The block diagram of 8-to-1 Mux is shown in Figure 1. A 2n-to-1 multiplexer needs n bit selection line to select one of the 2n inputs to the output.Figure 1. Block diagram of 8-to-1 multiplexer Truth Table

Figure 2 shows the truth table of the 8-to-1 multiplexer. I1 to I8 are the input lines, S1 - S3 are the selection lines and O is the output line.Figure 2. Truth table of 8-to-1 multiplexer Verilog Module

Figure 3 shows the Verilog module of the 8-to-1 multiplexer. The 8-bit ports In1 to In8 are input lines of the multiplexer. The Sel port is the 3-bit selection line which is required to select between the eight input lines. 8-bit port Out is the output line of the multiplexer.Figure 3. Verilog module of 8-to-1 multiplexer Verilog Code for the 8-to-1 Multiplexer (mux8to1.v)

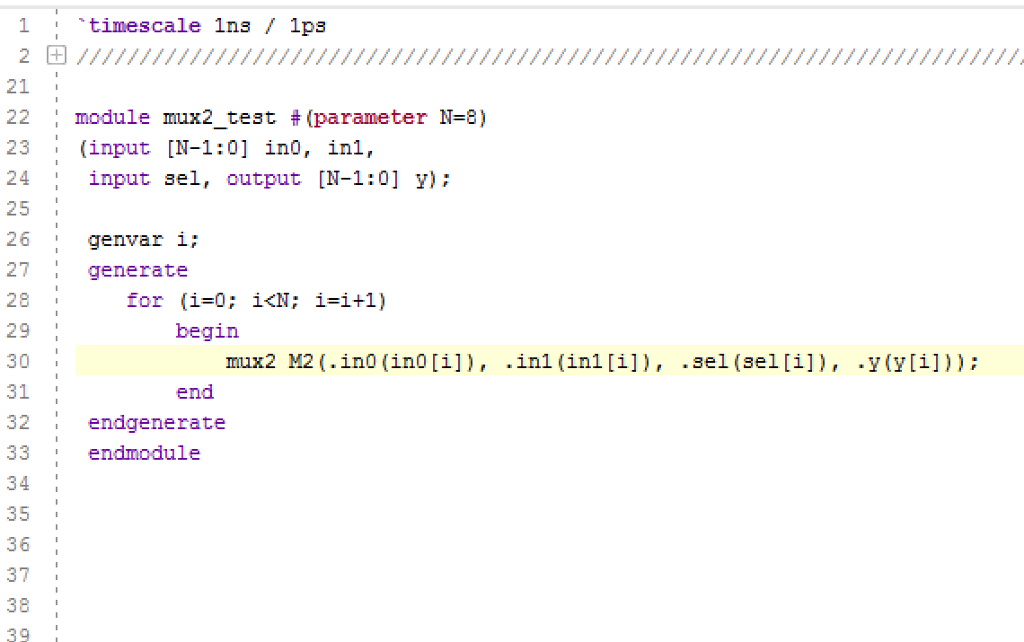

Figure 4. Verilog Code for 8-to-1 multiplexer Verilog Test Bench for 8-to-1 Multiplexer (mux8to1_tb.v)

Figure 5. Verilog Test-Bench for 8-to-1 multiplexer Timing Diagram

Figure 6. Timing diagram of 8-to-1 multiplexer

8 to 1 Multiplexer HDL Verilog Code

This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using verilog.

Symbol

Following is the symbol and truth table of 8 to 1 Multiplexer.

Truth Table

Verilog code

module mux8_1

input [7:0]I;

output [2:0]S;

output y;

input en;

reg y;

always @(en,S,I,y);

begin

if (en= =1)

begin

if (s= =000 y=I[0];

else if (s001) y=I[1];

else if (s001) y=I[2];

else if (s001) y=I[3];

else if (s001) y=I[4];

else if (s001) y=I[5];

else if (s001) y=I[6];

else if (s001) y=I[7];

end

else y=0;

end

end

end module

Simulation result

RF and Wireless tutorials